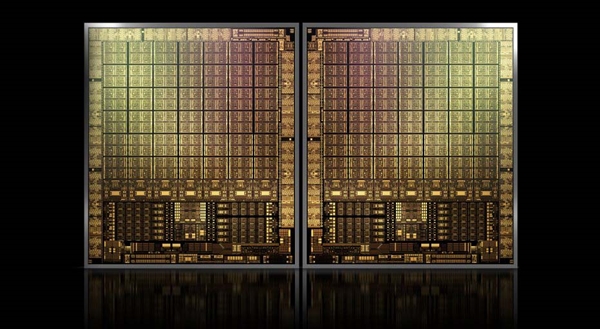

據(jù)媒體報(bào)道,NVIDIA下一代主要面向高性能計(jì)算、人工智能等Hopper架構(gòu),將會(huì)采用5nm工藝制程,晶體管多達(dá)1400億個(gè),面積核心達(dá)到了900平方毫米,是有史以來最大的GPU。

作為參考,NVIDIA自家旗艦Ampere架構(gòu)的A100為542億個(gè)晶體管(每平方毫米約為6560萬個(gè)晶體管),AMD陣營(yíng)中采用Aldebaran架構(gòu)的Instinct MI200系列為582億個(gè)晶體管(每平方米約為7360萬個(gè)晶體管),GH100是它們的2.5倍左右。

Hopper架構(gòu)的GH100在5nm的加持下,能夠在單芯片封裝下輕松做到每平方毫米1.5億個(gè)晶體管。

不過這一說法遭到了存疑,因?yàn)楫?dāng)前EUV光罩的限制為858平方毫米,而GH100核心的900平方毫米略大了一些。

還有消息稱,英偉達(dá)會(huì)在這一代GPU產(chǎn)品線中嘗試多芯片封裝(MCM),并稱之為GH102,會(huì)以獨(dú)立的SKU出現(xiàn)。

以上說法還未得到官方證實(shí),不過已經(jīng)確定的是,NVIDIA將于2022年3月21日發(fā)布GTC 2022大會(huì),屆時(shí)可能會(huì)公布關(guān)于基于下一代計(jì)算架構(gòu)“Hopper”,以及相應(yīng)的加速計(jì)算卡方案。

特別提醒:本網(wǎng)信息來自于互聯(lián)網(wǎng),目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)。其原創(chuàng)性以及文中陳述文字和內(nèi)容未經(jīng)本站證實(shí),對(duì)本文以及其中全部或者部分內(nèi)容、文字的真實(shí)性、完整性、及時(shí)性本站不作任何保證或承諾,并請(qǐng)自行核實(shí)相關(guān)內(nèi)容。本站不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。如若本網(wǎng)有任何內(nèi)容侵犯您的權(quán)益,請(qǐng)及時(shí)聯(lián)系我們,本站將會(huì)在24小時(shí)內(nèi)處理完畢。

站長(zhǎng)資訊網(wǎng)

站長(zhǎng)資訊網(wǎng)